企业博客

更多>>压控振荡器绝对拉动范围

来源:http://www.kangbidz.com 作者:康比电子 2019年04月04

VCXO晶振是一种晶体振荡器,在用石英晶体稳频的振荡器中,把变容二极管和石英晶体相串接,就可形成晶体压控振荡器.为了扩大调频范围,石英晶体可用AT切割和取用其基频率的石英晶体,在电路上还可采用展宽调频范围的变换网络.在微波频段,用反射极电压控制频率的反射速调管振荡器和用阳极电压控制频率的磁控管振荡器等也都属于压控振荡器的性质.压控振荡器的应用范围很广.

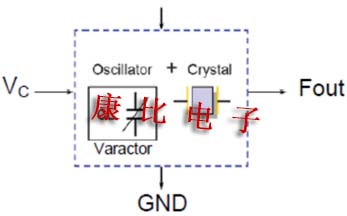

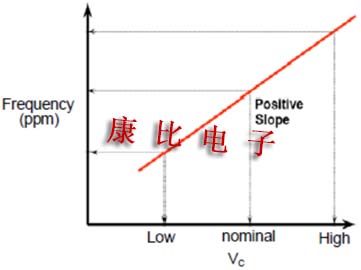

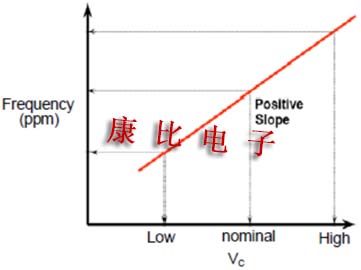

通过向其控制电压引脚(VC)施加模拟电压,其输出频率(Fout)可以在连续的频率范围内在任一方向上偏离标称值.控制电压与变容二极管相连.这种二极管的可变电容是所施加电压的函数.在图1和图2中,请注意,随着可变电容的变化,它会导致电容负载的变化.CL的变化导致Fout的变化.如图2所示,理想情况下,VC和Fout之间存在线性关系.

APR-当控制电压设置为最大和最小值时,VCXO振荡器与标称频率的保证正负频率偏差.它保证超过制造公差,电源电压,工作温度和老化.

APR通过从VCXO的总稳定性中减去总牵引范围来计算.总牵引范围是恒定电源电压和温度下,压控振荡器频率随控制电压变化的最大变化.总稳定性是指当控制电压在制造公差,电源电压,工作温度和老化变化范围内保持在标称值时,VCXO频率的变化.这种差异导致频率变化,这是由于控制电压独立于所有其他条件和变化而得到保证的.

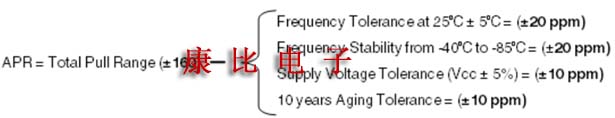

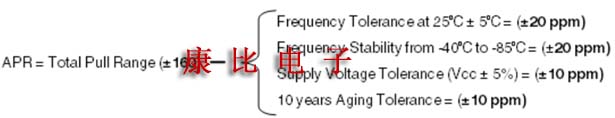

APR计算示例

APR是从VCXO的输出频率范围预算中得出的,该预算考虑了导致VCXO频率偏差的所有因素.请参考示例计算.

在本例中,以100ppm的APR为特征的压控振荡器意味着使用该VCXO的锁相环可以锁定到标称中心频率变化高达100ppm的输入基准.

在本例中,以100ppm的APR为特征的压控振荡器意味着使用该VCXO的锁相环可以锁定到标称中心频率变化高达100ppm的输入基准.

APR在锁相环设计中的应用

锁相环是使用负反馈的控制系统的一个例子,该负反馈产生与参考时钟晶体谐振器信号的相位具有固定关系的输出时钟信号.锁相环是作为一个基本问题的解决方案而开发的;如果需要一个比现有时钟频率更高的时钟,或者具有相同频率但抖动更低的时钟,或者具有更高频率和更低抖动的时钟,那么现有时钟上没有线性运算能够将现有时钟转换成所需时钟.相反,需要一个新的振荡器,它必须与现有时钟的频率和相位完全匹配.相位匹配要求需要负反馈环路.

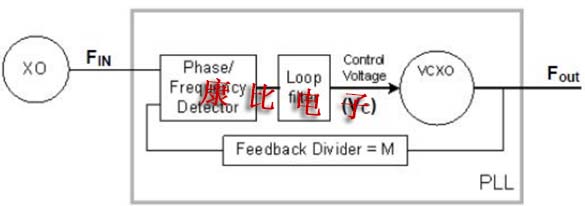

锁相环通过将压控振荡器时钟频率和相位除以反馈分频器(M)的值,并将其与相位/频率检测器中输入时钟频率和相位(FIN)的相位和频率进行比较,从而产生误差信号.相位/频率检测器的输出由环路滤波器进行低通滤波,以产生FOUT的控制电压调整,从而闭合环路.锁定时,锁相环的输出频率(FOUT)正好是输入频率的M时代,并与输入参考时钟相位对齐.如果Fout必须等于Fin,则添加值为M的后分频器或将M设置为1.

总之,以APR为特征的VCXO使锁相环设计者不必考虑影响VCXO中心频率的额外内部变化的细节.只需确保压控振荡器APR与锁相环输入基准电压的ppm变化一样大.

通过向其控制电压引脚(VC)施加模拟电压,其输出频率(Fout)可以在连续的频率范围内在任一方向上偏离标称值.控制电压与变容二极管相连.这种二极管的可变电容是所施加电压的函数.在图1和图2中,请注意,随着可变电容的变化,它会导致电容负载的变化.CL的变化导致Fout的变化.如图2所示,理想情况下,VC和Fout之间存在线性关系.

图1.典型VCXO

图2.典型拉动范围曲线

APR的定义APR-当控制电压设置为最大和最小值时,VCXO振荡器与标称频率的保证正负频率偏差.它保证超过制造公差,电源电压,工作温度和老化.

APR通过从VCXO的总稳定性中减去总牵引范围来计算.总牵引范围是恒定电源电压和温度下,压控振荡器频率随控制电压变化的最大变化.总稳定性是指当控制电压在制造公差,电源电压,工作温度和老化变化范围内保持在标称值时,VCXO频率的变化.这种差异导致频率变化,这是由于控制电压独立于所有其他条件和变化而得到保证的.

APR计算示例

APR是从VCXO的输出频率范围预算中得出的,该预算考虑了导致VCXO频率偏差的所有因素.请参考示例计算.

APR在锁相环设计中的应用

锁相环是使用负反馈的控制系统的一个例子,该负反馈产生与参考时钟晶体谐振器信号的相位具有固定关系的输出时钟信号.锁相环是作为一个基本问题的解决方案而开发的;如果需要一个比现有时钟频率更高的时钟,或者具有相同频率但抖动更低的时钟,或者具有更高频率和更低抖动的时钟,那么现有时钟上没有线性运算能够将现有时钟转换成所需时钟.相反,需要一个新的振荡器,它必须与现有时钟的频率和相位完全匹配.相位匹配要求需要负反馈环路.

锁相环通过将压控振荡器时钟频率和相位除以反馈分频器(M)的值,并将其与相位/频率检测器中输入时钟频率和相位(FIN)的相位和频率进行比较,从而产生误差信号.相位/频率检测器的输出由环路滤波器进行低通滤波,以产生FOUT的控制电压调整,从而闭合环路.锁定时,锁相环的输出频率(FOUT)正好是输入频率的M时代,并与输入参考时钟相位对齐.如果Fout必须等于Fin,则添加值为M的后分频器或将M设置为1.

图3.基本锁相环构建模块

由于石英晶体振荡器(XO)制造差异,输入基准频率FIN具有ppm容差.这包括容差,稳定性,电源电压和老化.VCXO的频率必须具有至少相同ppm变化的保证可调范围,以便跟踪和保持输入基准频率变化上的相位和频率锁定.由于压控振荡器本身是一个振荡器,由于制造公差,稳定性,电源电压和老化,其频率也会发生相同的变化.这些变化必须得到保证,并应从总拉动范围中减去.如果VCXO没有足够的APR,并且输入参考处于其中一个频率极值,锁相环将不会锁定,输出频率也不会是输入频率的M时代.总之,以APR为特征的VCXO使锁相环设计者不必考虑影响VCXO中心频率的额外内部变化的细节.只需确保压控振荡器APR与锁相环输入基准电压的ppm变化一样大.

正在载入评论数据...

此文关键字: VCXO振荡器石英晶体振荡器制造差异

相关资讯

- [2024-02-18]Greenray晶体振荡器专为国防和航...

- [2024-01-20]HELE加高产品和技术及热门应用

- [2024-01-20]HELE加高一个至关重要的组件晶体...

- [2023-12-28]Suntsu晶振最新的射频滤波器突破...

- [2023-12-28]Qantek提供各种高可靠性微处理器...

- [2023-10-11]日本纳卡石英晶体的低老化领先同...

- [2023-09-25]遥遥领先H.ELE开启汽车创新

- [2023-09-23]瑞萨电子MCU和MPU产品领先同行